# MITSUBISHI

## Type ACPU/QCPU-A (A Mode)

**Programming Manual (Fundamentals)**

## SAFETY CAUTIONS

(You must read these cautions before using the product)

In connection with the use of this product, in addition to carefully reading both this manual and the related manuals indicated in this manual, it is also essential to pay due attention to safety and handle the product correctly.

The safety cautions given here apply to this product in isolation. For information on the safety of the PLC system as a whole, refer to the CPU module User's Manual.

Store this manual carefully in a place where it is accessible for reference whenever necessary, and forward a copy of the manual to the end user.

#### REVISIONS

| Print Date | *Manual Number  | Revision                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Feb., 1991 | IB (NA) 66249-A | First edition                                                                                                                                                                                                                                                                                                                                                                                  |

| Sep., 1993 | IB (NA) 66249-B | Addition of models                                                                                                                                                                                                                                                                                                                                                                             |

|            |                 | A1SCPU, A2UCPU(S1), A3UCPU, A4UCPU,<br>A2ACPU(S1)-F, A3ACPU-F                                                                                                                                                                                                                                                                                                                                  |

|            |                 | Correction                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                 | CONTENTS, Section 1, 1.1, 2.1, 2.3.1, 2.4, 2.4.2, 2.4.3, 2.5, 2.6, 2.6.1, to 2.6.3, 3.1 to 3.6, 3.6.2, 3.6.3, 3.7, 3.7.1 to 3.7.4, 3.8, 3.8.2, 3.9 to 3.11, 3.11.2, 3.12, 3.13, 3.13.1, 3.13.2, 3.14 to 3.17, 4, 4.2, 4.2.2, 4.2.3, 4.3, 4.3.2, 4.4, 4.4.1, 5, 5.1, 5.1.1 to 5.1.3, 5.2, 5.2.1, 5.3, 5.3.1, 5.3.2, 5.3.4, 6, 6.1 to 6.8, 6.8.2, 6.8.3, 6.9 to 6.13, 6.13.1, 6.14 to 6.17, 7, 8 |

|            |                 | Addition                                                                                                                                                                                                                                                                                                                                                                                       |

|            |                 | Section 5.2.3, 6.18, 9 to 11                                                                                                                                                                                                                                                                                                                                                                   |

|            |                 | Deletion                                                                                                                                                                                                                                                                                                                                                                                       |

|            |                 | For BEGINNERS                                                                                                                                                                                                                                                                                                                                                                                  |

| Sep., 1990 | IB (NA) 66249-C | Correction                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                 | Section 3.11.2, 3.13.2, 4.2.2                                                                                                                                                                                                                                                                                                                                                                  |

| Dec., 1990 | IB (NA) 66249-D | Chapter 9 added                                                                                                                                                                                                                                                                                                                                                                                |

| May, 1991  | IB (NA) 66249-E | Correction                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                 | Section 3.6.3, 3.7.4, 3.13.1, 3.13.2, 4.4.1<br>A1SCPU added                                                                                                                                                                                                                                                                                                                                    |

| Feb., 1992 | IB (NA) 66249-F | Correction                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                 | Section 3.16, 9.1, 9.6                                                                                                                                                                                                                                                                                                                                                                         |

| Apr., 1992 | IB (NA) 66249-G | Correction                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                 | Section 3.5, 5.3.4, Chapter 8, Section 9.6                                                                                                                                                                                                                                                                                                                                                     |

| Aug., 1992 | IB (NA) 66249-H | Correction                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                 | Section 3.3                                                                                                                                                                                                                                                                                                                                                                                    |

| May, 1993  | IB (NA) 66249-1 | Correction                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                 | A2UCPU(S1), A3UCPU, A4UCPU, A52GCPU,<br>A373CPU added<br>Section 6.18, 9.7, 9.8, Chapter 10, 11 added                                                                                                                                                                                                                                                                                          |

| Aug., 1994 | IB (NA) 66249-J | Correction                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                 | Section 2.4.1, 2.4.2, Chapter 11                                                                                                                                                                                                                                                                                                                                                               |

| May, 1997  | IB (NA) 66249-K | Correction                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                 | Section 3.1, 3.3, 3.4, 3.5, 3.6.2, 3.10, 3.11.2, 5.3.4, 10.4.1, IMPORTANT                                                                                                                                                                                                                                                                                                                      |

|            |                 | Addition                                                                                                                                                                                                                                                                                                                                                                                       |

|            |                 | Section 3.11.1, 5.3.4, 6.1, Chapter 11                                                                                                                                                                                                                                                                                                                                                         |

\*The manual number is given on the bottom left of the back cover.

This manual does not imply guarantee or implementation right for industrial ownership or implementation of other rights. Mitsubishi Electric Corporation is not responsible for industrial ownership problems caused by use of the contents of this manual.

| Print Date | *Manual Number  | Revision                                                                                                                                            |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Aug., 1998 | IB (NA) 66249-L | Addition of models                                                                                                                                  |

|            |                 | A1SJCPU-S3, A1SCPUC24-R2, A2SCPU(S1),<br>A1SHCPU, A1SJHCPU, A2SHCPU(S1),<br>A2ASCPU(S1), A1FXCPU                                                    |

|            |                 | Addition                                                                                                                                            |

|            |                 | Section 4.5, Appendix 1                                                                                                                             |

|            |                 | Correction                                                                                                                                          |

|            |                 | CONTENTS, Section 1.1, 3.1, 4.3.1, Chapter 5,<br>Section 6.9, 6.10, 6.11, 9.1, 9.3 to 9.12, 10.3                                                    |

|            |                 | Deletion                                                                                                                                            |

|            |                 | A2NCPU(P21/R21)-F, A2NCPU(P21/R21)-S1-F,<br>A3NCPU(P21/R21)-F, A3N Board                                                                            |

| Feb., 2000 | IB (NA) 66249-M | The manual name is changed into ACPU/QCPU-A(A<br>Mode) Programming Manual (Fundamentals).<br>[Old name: ACPU Programming Manual<br>(Fundamentals).] |

|            |                 | Addition of models                                                                                                                                  |

|            |                 | Q02CPU-A, Q02HCPU-A, Q06HCPU-A, A2USHCPU-S1, A1SJHCPU-S8                                                                                            |

| Dec., 2000 | IB (NA) 66249-N | Correction                                                                                                                                          |

|            |                 | Section 3.1, 3.6.2, Chapter 8                                                                                                                       |

| Jul., 2002 | IB (NA) 66249-O | Correction                                                                                                                                          |

|            |                 | Section 3.1, 6.9                                                                                                                                    |

| Dec., 2003 | IB (NA) 66249-P | Correction                                                                                                                                          |

|            |                 | Section 3.1, 3.7, 3.17                                                                                                                              |

| Mar., 2006 | IB (NA) 66249-Q | Addition                                                                                                                                            |

|            |                 | Appendix 2                                                                                                                                          |

|            |                 |                                                                                                                                                     |

|            |                 | Section 3.2,5.3, 5.3.5, 6.3, 6.4, 9.2, 9.4, 9.6, 9.7, 9.8, 9.9, 9.10, 9.11, 9.12, 9.13, Appendix 1                                                  |

| Jun., 2007 | IB (NA) 66249-R | Correction                                                                                                                                          |

|            |                 | Section 6.9, 6.18                                                                                                                                   |

|            |                 |                                                                                                                                                     |

|            |                 |                                                                                                                                                     |

|            |                 |                                                                                                                                                     |

|            |                 |                                                                                                                                                     |

|            |                 |                                                                                                                                                     |

|            |                 |                                                                                                                                                     |

|            |                 |                                                                                                                                                     |

|            |                 |                                                                                                                                                     |

Japanese Manual Version SH-3435-U

This manual does not imply guarantee or implementation right for industrial ownership or implementation of other rights. Mitsubishi Electric Corporation is not responsible for industrial ownership problems caused by use of the contents of this manual.

### CONTENTS

| 1. | GENE | ERAL D                                                            | ESCRIPTION 1 – 1                                                                                                                                                                                                                                                                                  |

|----|------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 1.1  | CPU T                                                             | ypes and Their Abbreviations Used in this Manual $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 1 - 1$                                                                                                                                                                                         |

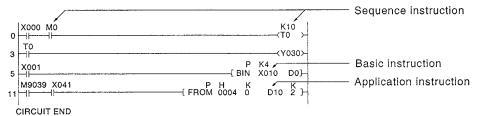

| 2. | PROC | GRAMM                                                             | 11NG LANGUAGES AND OPERATIONS. $2 - 1 \sim 2 - 19$                                                                                                                                                                                                                                                |

|    | 2.1  | Progra                                                            | mming Languages                                                                                                                                                                                                                                                                                   |

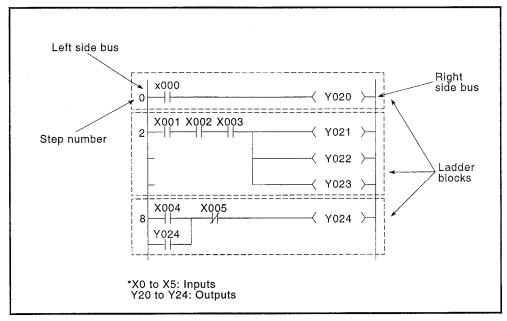

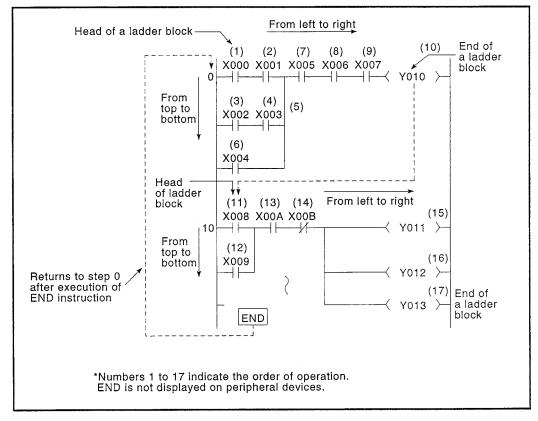

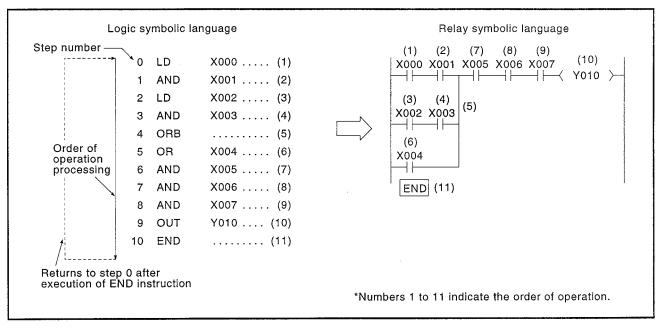

|    |      | 2.1.1                                                             | Relay symbolic language (ladder mode)                                                                                                                                                                                                                                                             |

|    |      | 2.1.2                                                             | Logic symbolic language (list mode)2-4                                                                                                                                                                                                                                                            |

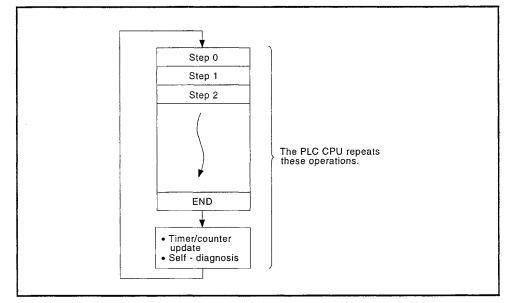

|    | 2.2  | Operat                                                            | tion Processing of the PLC CPU                                                                                                                                                                                                                                                                    |

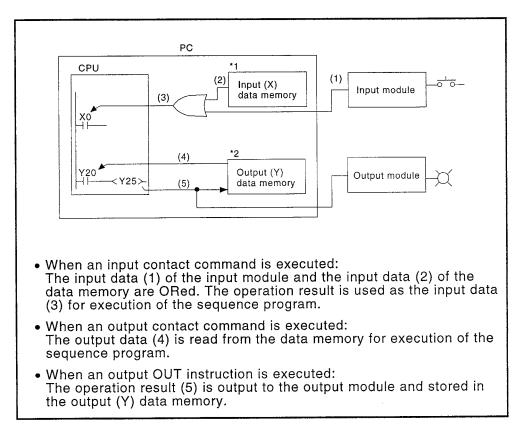

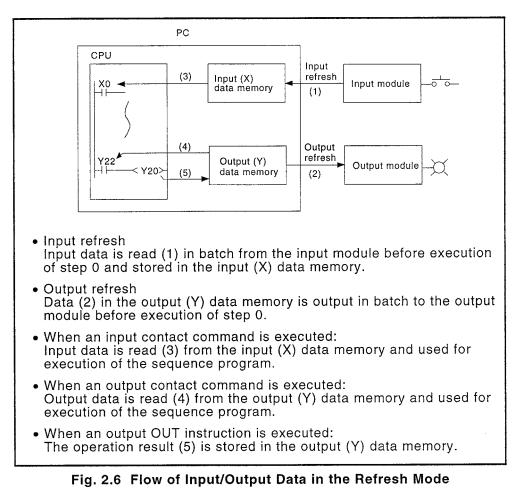

|    | 2.3  | Input a                                                           | Ind Output Processings                                                                                                                                                                                                                                                                            |

|    |      | 2.3.1                                                             | Direct mode                                                                                                                                                                                                                                                                                       |

|    |      | 2.3.2                                                             | Refresh mode                                                                                                                                                                                                                                                                                      |

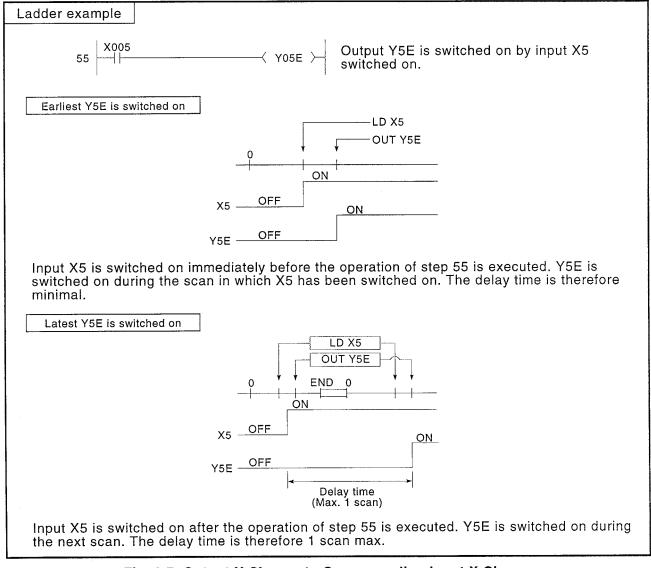

|    | 2.4  | Respo                                                             | nse Lag                                                                                                                                                                                                                                                                                           |

|    |      | 2.4.1                                                             | In the direct mode                                                                                                                                                                                                                                                                                |

|    |      | 2.4.2                                                             | In the refresh mode                                                                                                                                                                                                                                                                               |

|    |      | 2.4.3                                                             | Response when direct and refresh modes are switched                                                                                                                                                                                                                                               |

|    | 2.5  | Scan T                                                            |                                                                                                                                                                                                                                                                                                   |

|    | 2.6  |                                                                   | ic Data Usable for Sequence Programs                                                                                                                                                                                                                                                              |

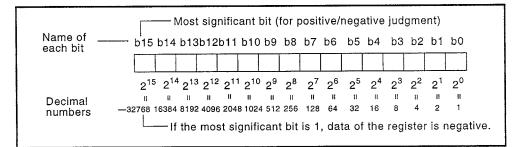

|    |      | 2.6.1                                                             | Binary notation                                                                                                                                                                                                                                                                                   |

|    |      | 2.6.2                                                             | Hexadecimal                                                                                                                                                                                                                                                                                       |

|    |      | 2.6.3                                                             | BCD (Binary-coded decimal)                                                                                                                                                                                                                                                                        |

|    |      |                                                                   | 202 (2)                                                                                                                                                                                                                                                                                           |

| 3. | DEVI | CES                                                               | 3 – 1 ~ 3 – 58                                                                                                                                                                                                                                                                                    |

|    | 3.1  | List of                                                           | Devices                                                                                                                                                                                                                                                                                           |

|    | 3.2  | Input ()                                                          | X) and Output (Y)                                                                                                                                                                                                                                                                                 |

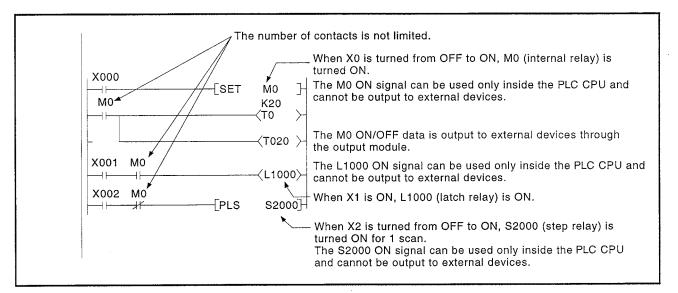

|    | 3.3  |                                                                   | al Relays (M), Latch Relays (L), and Step Relays (S)                                                                                                                                                                                                                                              |

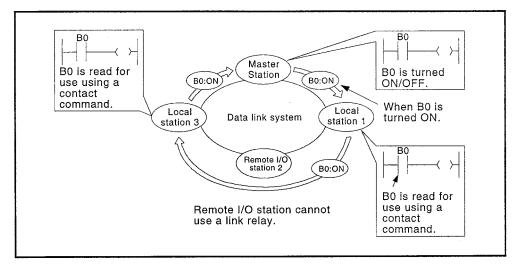

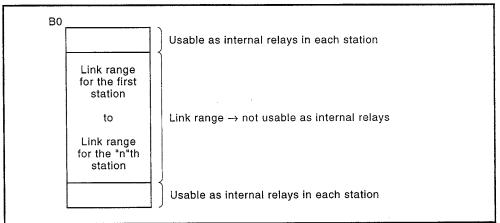

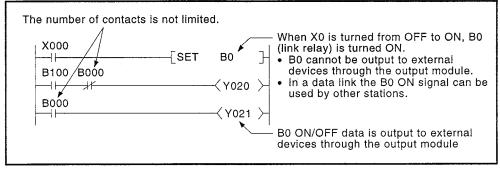

|    | 3.4  |                                                                   | elays (B)                                                                                                                                                                                                                                                                                         |

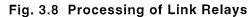

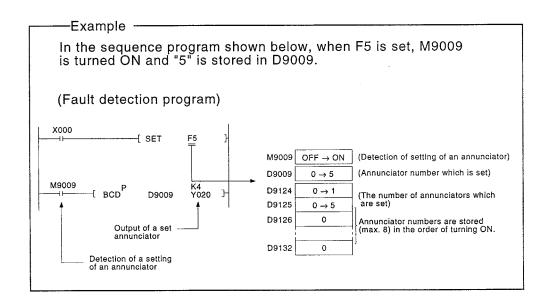

|    | 3.5  |                                                                   | ciators (F)                                                                                                                                                                                                                                                                                       |

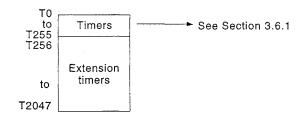

|    | 3.6  | Timers                                                            | s (T) 3 – 15                                                                                                                                                                                                                                                                                      |

|    |      | 3.6.1                                                             | 100 ms timers, 10 ms timers, and 100 ms retentive timers $\ldots \ldots 3 - 15$                                                                                                                                                                                                                   |

|    |      | 3.6.2                                                             | Processing and accuracy of timers                                                                                                                                                                                                                                                                 |

|    |      | 3.6.3                                                             | Extension timers                                                                                                                                                                                                                                                                                  |

|    |      | 3.6.4                                                             | 1ms timer                                                                                                                                                                                                                                                                                         |

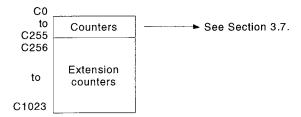

|    | 3.7  | Counte                                                            | ers (C)                                                                                                                                                                                                                                                                                           |

|    |      | 3.7.1                                                             | Count processing in direct mode                                                                                                                                                                                                                                                                   |

|    |      |                                                                   |                                                                                                                                                                                                                                                                                                   |

|    |      | 3.7.2                                                             | Count processing in refresh mode                                                                                                                                                                                                                                                                  |

|    |      |                                                                   | Count processing in refresh mode                                                                                                                                                                                                                                                                  |

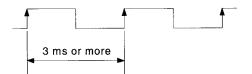

|    |      | 3.7.3                                                             | Maximum counting speed                                                                                                                                                                                                                                                                            |

|    | 3.8  | 3.7.3<br>3.7.4                                                    | Maximum counting speed    3 - 30      Extension counters    3 - 31                                                                                                                                                                                                                                |

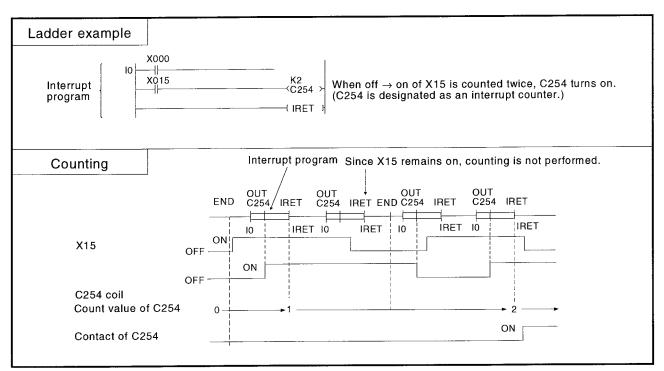

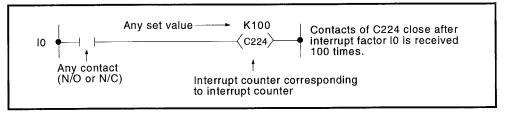

|    | 3.8  | 3.7.3<br>3.7.4<br>Interru                                         | Maximum counting speed.         3 - 30           Extension counters         3 - 31           pt Counters (C)         3 - 33                                                                                                                                                                       |

|    | 3.8  | 3.7.3<br>3.7.4<br>Interru<br>3.8.1                                | Maximum counting speed3 - 30Extension counters3 - 31pt Counters (C)3 - 33Counters for interrupt programs3 - 33                                                                                                                                                                                    |

|    |      | 3.7.3<br>3.7.4<br>Interru<br>3.8.1<br>3.8.2                       | Maximum counting speed       3 - 30         Extension counters       3 - 31         pt Counters (C)       3 - 33         Counters for interrupt programs       3 - 33         Counters for counting the number of interrupts (Interrupt counters)       3 - 35                                    |

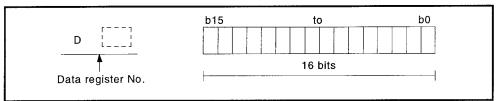

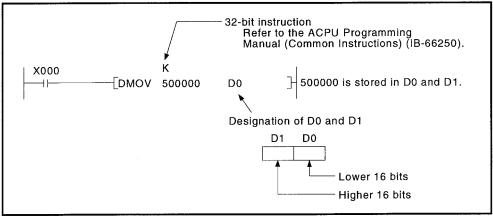

|    | 3.9  | 3.7.3<br>3.7.4<br>Interrup<br>3.8.1<br>3.8.2<br>Data R            | Maximum counting speed       3 - 30         Extension counters       3 - 31         pt Counters (C)       3 - 33         Counters for interrupt programs       3 - 33         Counters for counting the number of interrupts (Interrupt counters)       3 - 35         Registers (D)       3 - 38 |

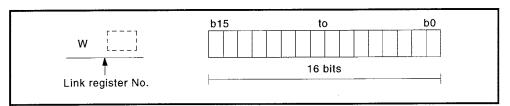

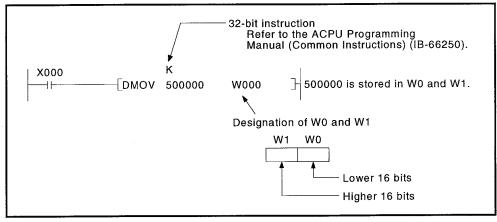

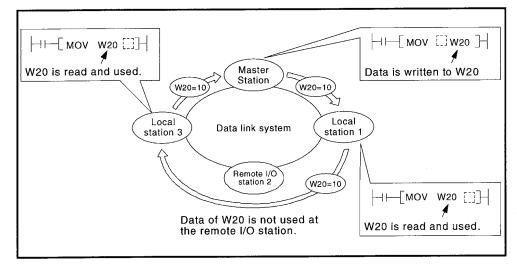

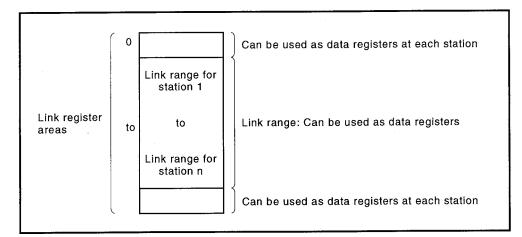

|    |      | 3.7.3<br>3.7.4<br>Interrup<br>3.8.1<br>3.8.2<br>Data R<br>Link Re | Maximum counting speed       3 - 30         Extension counters       3 - 31         pt Counters (C)       3 - 33         Counters for interrupt programs       3 - 33         Counters for counting the number of interrupts (Interrupt counters)       3 - 35                                    |

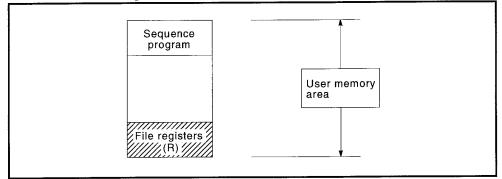

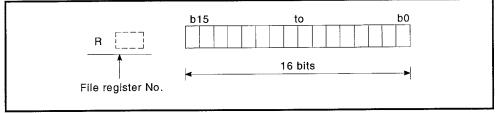

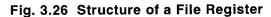

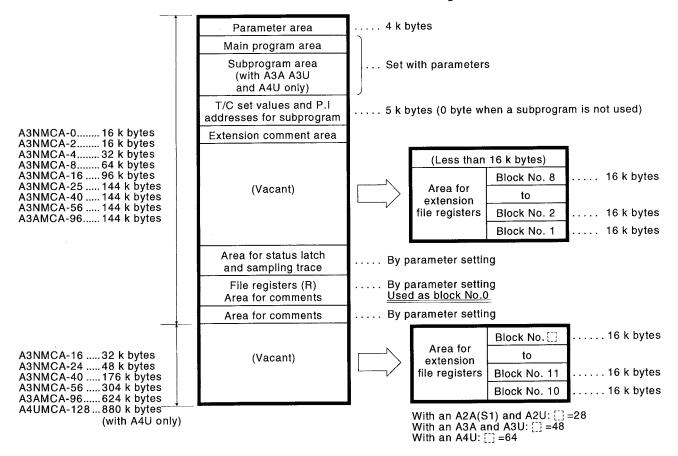

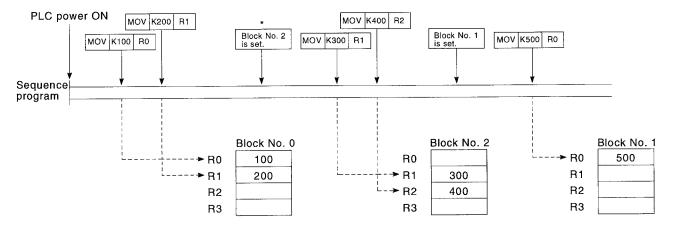

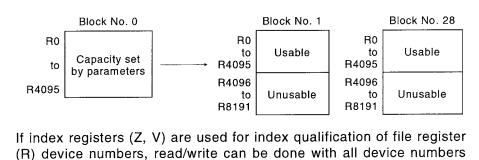

|    |                          | 3.11.1                                                                                                                                   | File registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                          | 3.11.2                                                                                                                                   | Extension file registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

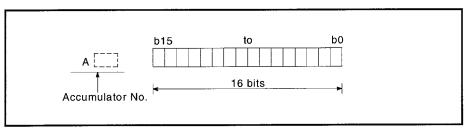

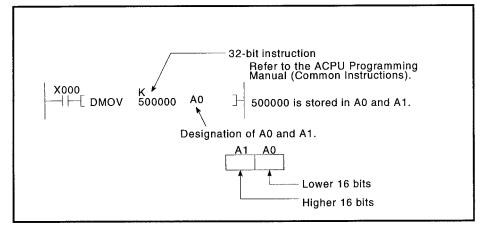

|    | 3.12                     | Accum                                                                                                                                    | ulators (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

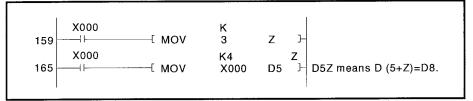

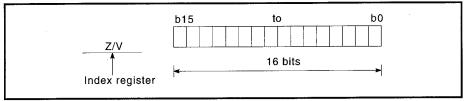

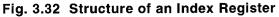

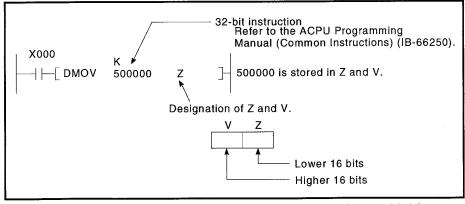

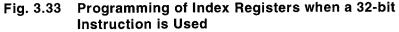

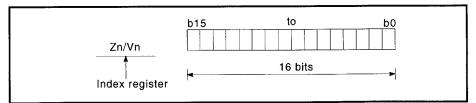

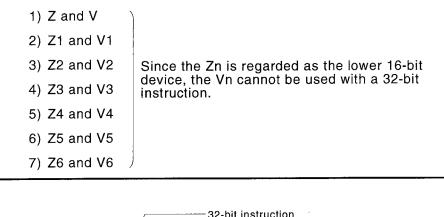

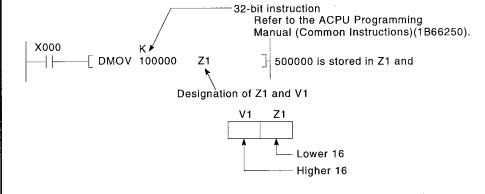

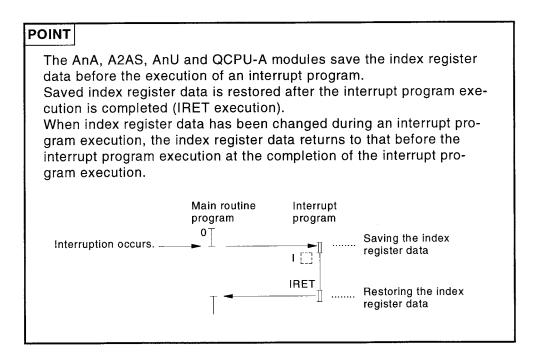

|    | 3.13                     | Index F                                                                                                                                  | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    |                          | 3.13.1                                                                                                                                   | Index registers (Z, V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    |                          | 3.13.2                                                                                                                                   | Index registers (Zn(Z, Z1 to Z6), Vn(V, V1 to V6))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

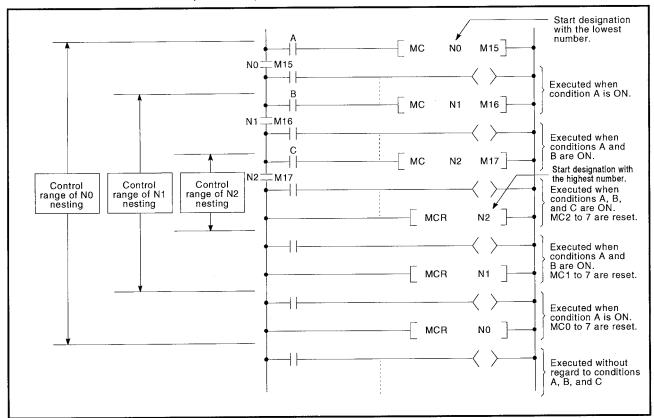

|    | 3.14                     | Nesting                                                                                                                                  | g (N)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

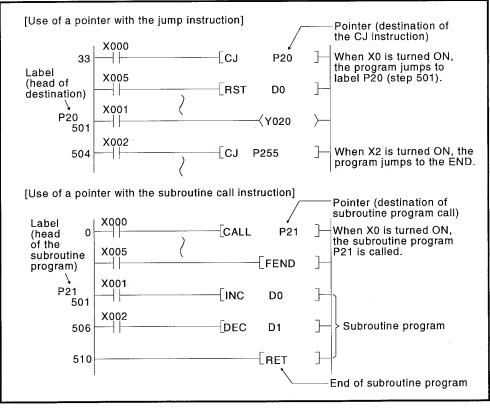

|    | 3.15                     |                                                                                                                                          | s (P)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

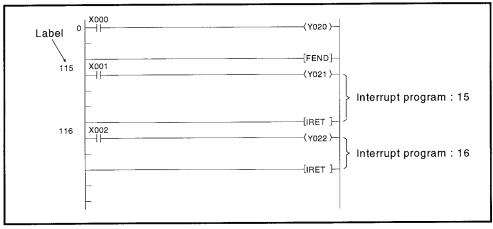

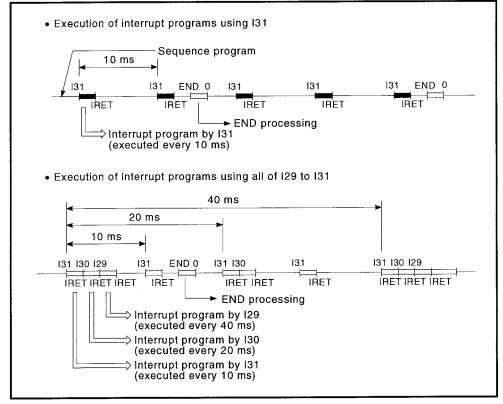

|    | 3.16                     |                                                                                                                                          | ot Pointers (I)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 3.17                     | Specia                                                                                                                                   | I Relays and Special Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

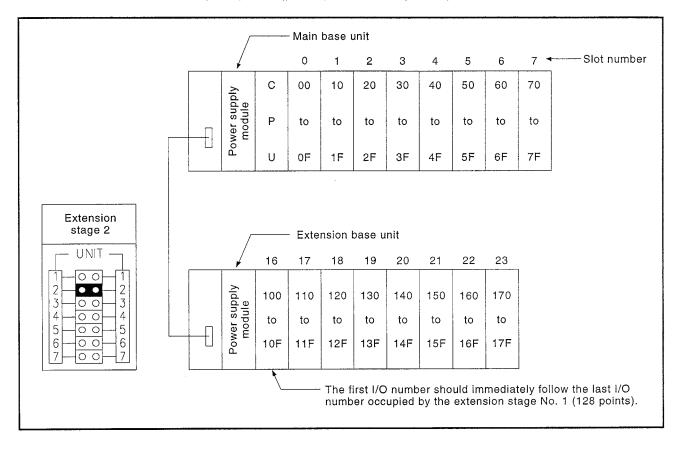

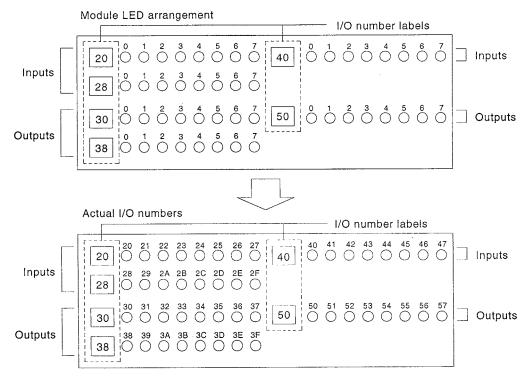

| 4. | ALLC                     | OCATIO                                                                                                                                   | N OF I/O NUMBERS 4 – 1 ~ 4 – 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 4.1                      | I/O Nu                                                                                                                                   | mbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

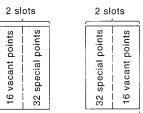

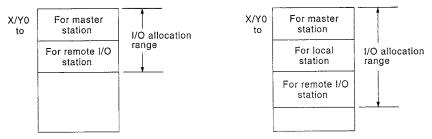

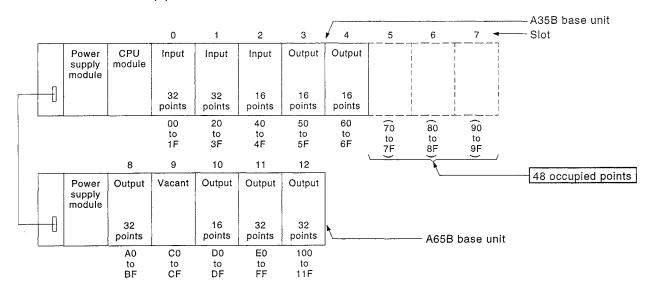

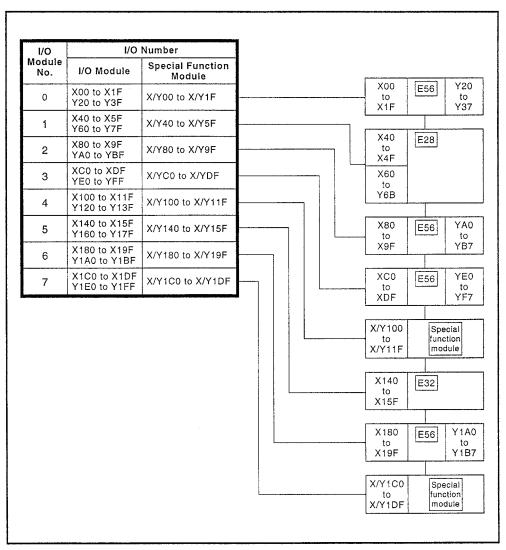

|    | 4.2                      |                                                                                                                                          | nber Allocation of the Building-block Type CPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

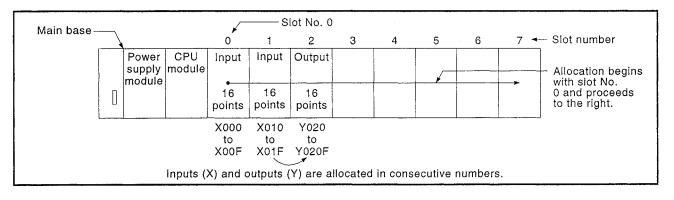

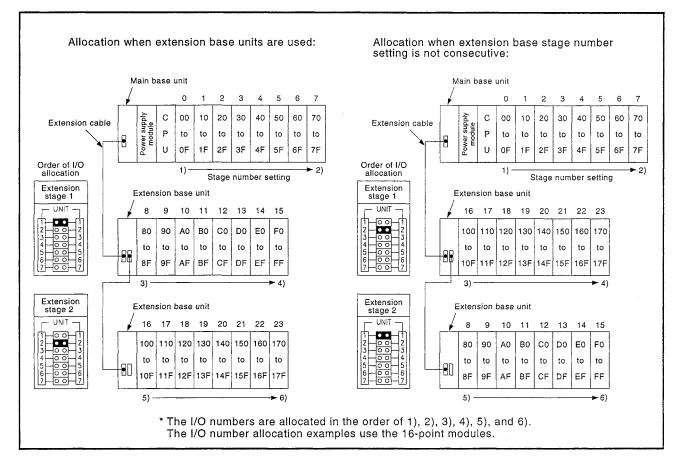

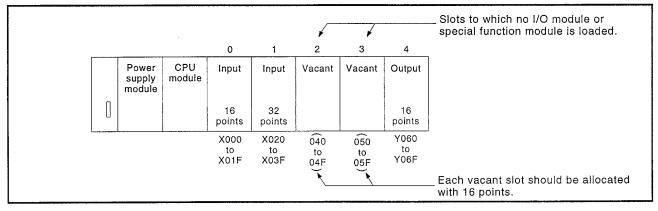

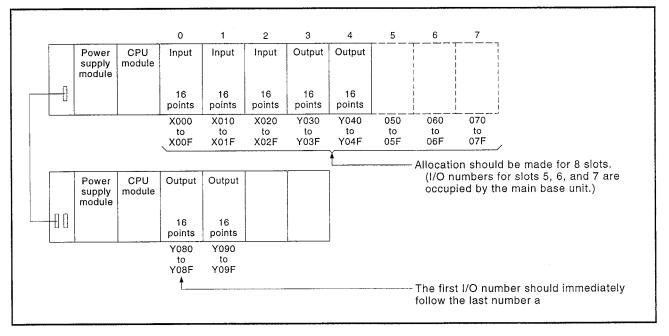

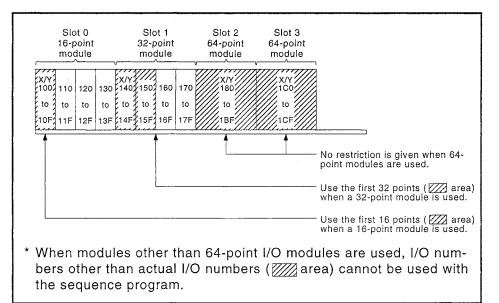

|    |                          | 4.2.1                                                                                                                                    | Basics of the I/O number allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    |                          | 4.2.2                                                                                                                                    | I/O allocation using peripheral devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

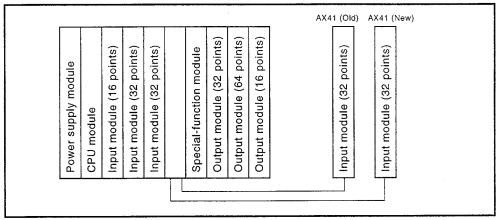

|    |                          | 4.2.3                                                                                                                                    | Example of I/O number allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

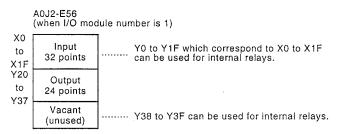

|    | 4.3                      | I/O Allo                                                                                                                                 | cation of the A0J2HCPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    |                          | 4.3.1                                                                                                                                    | Basics of I/O allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |                          | 4.3.2                                                                                                                                    | Example of I/O number allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

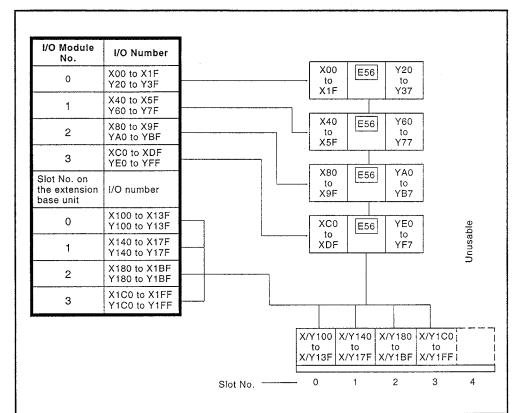

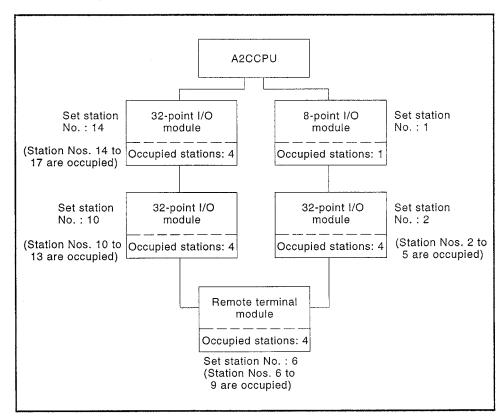

|    | 4.4                      | I/O Allo                                                                                                                                 | cation of the A2CCPU 4 – 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|    |                          | 4.4.1                                                                                                                                    | Basics of I/O allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |                          |                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

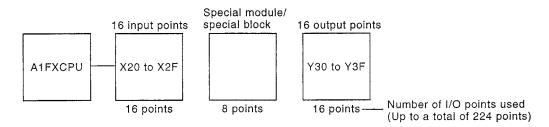

|    | 4.5                      | I/O Nu                                                                                                                                   | mber Assignment for A1FXCPU4 – 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    | 4.5                      | I/O Nui<br>4.5.1                                                                                                                         | nber Assignment for A1FXCPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

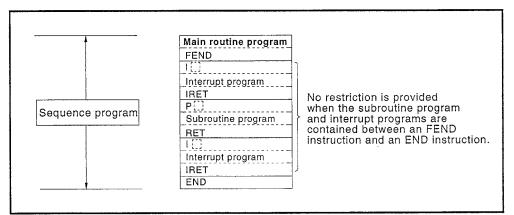

| 5. |                          | 4.5.1                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5. | PROC                     | 4.5.1<br>GRAM S                                                                                                                          | I/O number assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

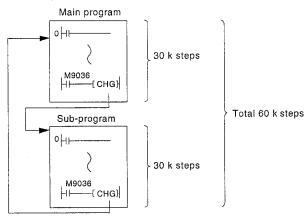

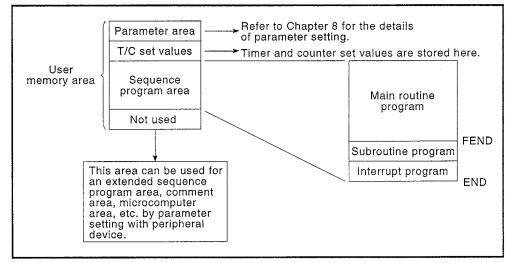

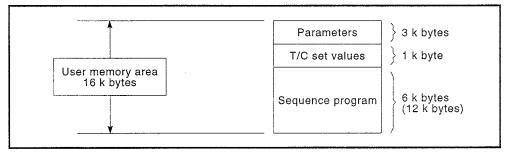

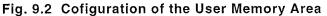

| 5. |                          | 4.5.1<br>GRAM S<br>Seque                                                                                                                 | I/O number assignment.       4 – 18         STRUCTURE.       5 – 1 ~ 5 – 24         nce Program       5 – 2 – 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

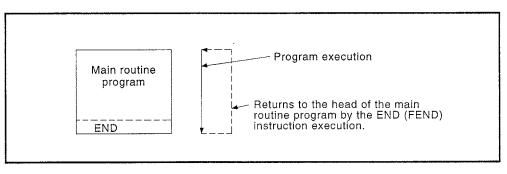

| 5. | PROC                     | 4.5.1<br>GRAM S<br>Sequer<br>5.1.1                                                                                                       | I/O number assignment.       4 – 18         STRUCTURE.       5 – 1 ~ 5 – 24         nce Program       5 – 2         Main routine program       5 – 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

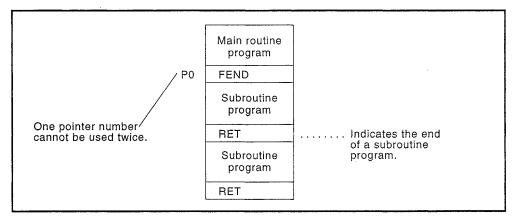

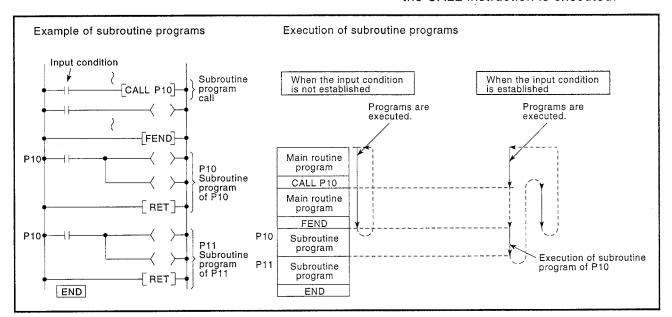

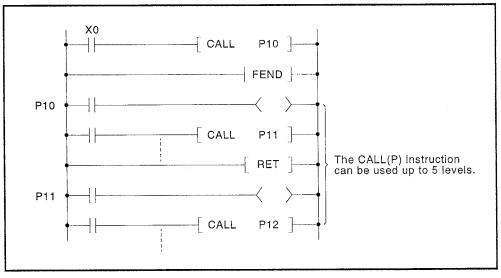

| 5. | PROC                     | 4.5.1<br>GRAM S<br>Sequer<br>5.1.1<br>5.1.2                                                                                              | I/O number assignment.       4 – 18         STRUCTURE.       5 – 1 ~ 5 – 24         nce Program       5 – 2         Main routine program       5 – 3         Subroutine program       5 – 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

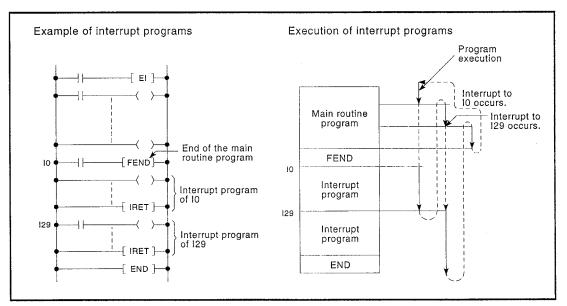

| 5. | <b>PRO</b><br>5.1        | 4.5.1<br>GRAM S<br>Sequer<br>5.1.1<br>5.1.2<br>5.1.3                                                                                     | I/O number assignment.       4 – 18         STRUCTURE.       5 – 1 ~ 5 – 24         nce Program       5 – 2         Main routine program       5 – 3         Subroutine program       5 – 4         Interrupt programs       5 – 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

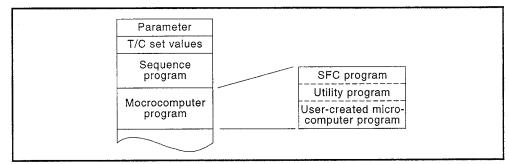

| 5. | PROC                     | 4.5.1<br>GRAM S<br>Sequer<br>5.1.1<br>5.1.2<br>5.1.3                                                                                     | I/O number assignment.       4 – 18         STRUCTURE.       5 – 1 ~ 5 – 24         Ince Program       5 – 2         Main routine program       5 – 3         Subroutine program       5 – 4         Interrupt programs       5 – 7         omputer Programs       5 – 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5. | <b>PRO</b><br>5.1        | 4.5.1<br>GRAM S<br>Sequen<br>5.1.1<br>5.1.2<br>5.1.3<br>Microce                                                                          | I/O number assignment.       4 – 18         STRUCTURE.       5 – 1 ~ 5 – 24         nce Program       5 – 2         Main routine program       5 – 3         Subroutine program       5 – 4         Interrupt programs       5 – 7         omputer Programs       5 – 12         Utility program       5 – 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5. | <b>PRO</b><br>5.1        | 4.5.1<br><b>GRAM S</b><br>Sequen<br>5.1.1<br>5.1.2<br>5.1.3<br>Microcol<br>5.2.1                                                         | I/O number assignment.       4 – 18         STRUCTURE.       5 – 1 ~ 5 – 24         Ince Program       5 – 2         Main routine program       5 – 3         Subroutine program       5 – 4         Interrupt programs       5 – 7         omputer Programs       5 – 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5. | <b>PRO</b><br>5.1        | 4.5.1<br><b>GRAM S</b><br>Sequent<br>5.1.1<br>5.1.2<br>5.1.3<br>Microcol<br>5.2.1<br>5.2.2<br>5.2.3                                      | I/O number assignment.       4 – 18         STRUCTURE.       5 – 1 ~ 5 – 24         nce Program       5 – 2         Main routine program       5 – 3         Subroutine program       5 – 4         Interrupt programs       5 – 7         omputer Programs       5 – 12         Utility program       5 – 13         User-created microcomputer program       5 – 13         SFC program       5 – 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

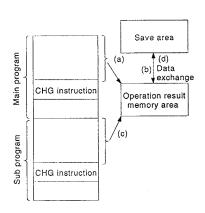

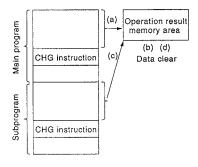

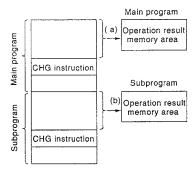

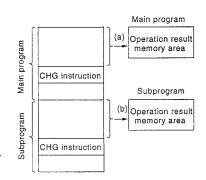

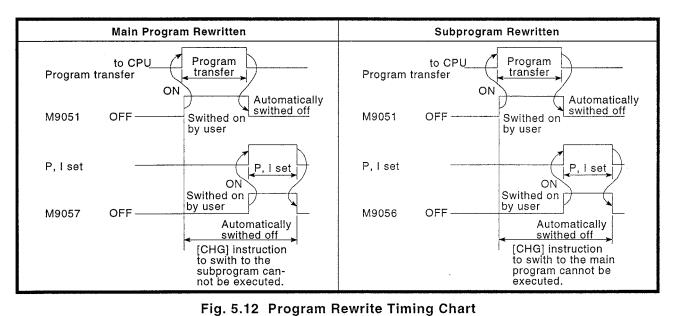

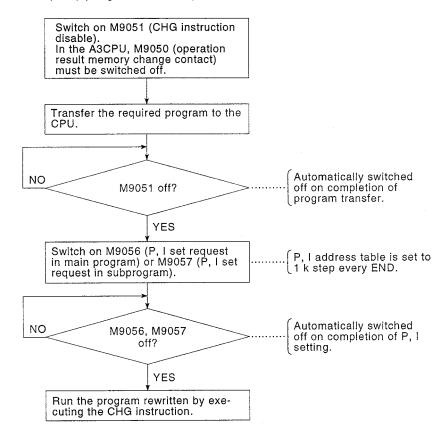

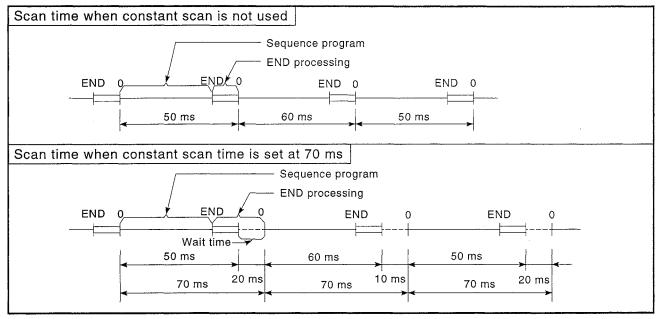

| 5. | <b>PRO</b><br>5.1<br>5.2 | 4.5.1<br><b>GRAM S</b><br>Sequent<br>5.1.1<br>5.1.2<br>5.1.3<br>Microcol<br>5.2.1<br>5.2.2<br>5.2.3                                      | I/O number assignment.       4 – 18         STRUCTURE.       5 – 1 ~ 5 – 24         Ince Program       5 – 2         Main routine program       5 – 3         Subroutine program       5 – 4         Interrupt programs       5 – 7         omputer Programs       5 – 12         Utility program.       5 – 13         User-created microcomputer program       5 – 13         SFC program       5 – 13         Use the Sub-Programs       5 – 13         Use the Sub-Programs       5 – 15         When the CHG instruction is executed at the leading edge of the input and the execution/non-execution result storage memory is used                                                                                                                                                                                                                                                                                                                                                                                                          |